# Федеральное государственное бюджетное учреждение науки Институт системного программирования Российской академии наук

На правах рукописи

#### Татарников Андрей Дмитриевич

#### АВТОМАТИЗАЦИЯ КОНСТРУИРОВАНИЯ ГЕНЕРАТОРОВ ТЕСТОВЫХ ПРОГРАММ ДЛЯ МИКРОПРОЦЕССОРОВ НА ОСНОВЕ ФОРМАЛЬНЫХ СПЕЦИФИКАЦИЙ

Специальность 05.13.11 — математическое и программное обеспечение вычислительных машин, комплексов и компьютерных сетей

ДИССЕРТАЦИЯ на соискание ученой степени кандидата технических наук

Научный руководитель к.ф.-м.н. Камкин Александр Сергеевич

# Содержание

| Введение                                                              | 5    |

|-----------------------------------------------------------------------|------|

| Глава 1. Генерация тестовых программ для микропроцессоров             | . 15 |

| 1.1 Проектирование микропроцессоров                                   | . 15 |

| 1.2 Функциональная верификация микропроцессоров                       | . 18 |

| 1.3 Техники генерации тестовых программ                               | 22   |

| 1.4 Инструменты генерации тестовых программ                           | 26   |

| 1.4.1 Инструменты НИИСИ РАН                                           | 26   |

| 1.4.2 Инструменты ARM                                                 | 28   |

| 1.4.3 Инструменты IBM Research                                        | 30   |

| 1.4.4 Разработки ИСП РАН                                              | .34  |

| 1.4.5 Другие разработки                                               | 36   |

| 1.5 Выводы                                                            | .40  |

| Глава 2. Автоматизация конструирования генераторов тестовых программ  | .45  |

| 2.1 Метод автоматизации конструирования генераторов тестовых программ | ı 46 |

| 2.1.1 Использование формальных спецификаций                           | .46  |

| 2.1.2 Описание архитектуры микропроцессора на языке nML               | 47   |

| 2.1.3 Расширение возможностей языка nML                               | . 53 |

| 2.1.4 Архитектура модели микропроцессора                              | . 54 |

| 2.2 Язык описания шаблонов тестовых программ                          | 56   |

| 2.2.1 Структура тестовых программ                                     | .56  |

| 2.2.2 Описываемые свойства тестовых программ                          | 57   |

| 2.2.3 Концепция языка описания шаблонов тестовых программ             | . 59 |

| 2.2.4 Описание последовательностей команд                             | . 62 |

| 2.2.5 Описание правил выбора регистров                                | . 64 |

| 2.2.6 Описание тестовых ситуаций                                      | . 66 |

| 2.2.7 Описание инициализирующего кода и встроенных проверок           | . 67 |

| 2.2.8 Описание правил рандомизации                                    | .72  |

| 2.2.9 Описание размещения команд и данных в памяти                    | .74  |

| 2.2.10 Описание структуры переходов между тестовыми примерами         | 75   |

| 2.2.11 Расширяемость языка описания шаблонов тестовых программ | 76  |

|----------------------------------------------------------------|-----|

| 2.3 Архитектура генераторов тестовых программ                  | 77  |

| 2.3.1 Анализатор шаблонов тестовых программ                    | 78  |

| 2.3.2 Обработчик внутреннего представления                     | 80  |

| 2.3.3 Итератор последовательностей команд                      | 83  |

| 2.3.4 Обработчик последовательностей команд                    | 90  |

| 2.3.5 Расширяемость генератора тестовых программ               | 94  |

| 2.4 Выводы                                                     | 94  |

| Глава 3. Реализация предложенного метода                       | 95  |

| 3.1 Среда моделирования                                        | 96  |

| 3.1.1 Модель микропроцессора                                   | 96  |

| 3.1.2 Анализаторы формальных спецификаций                      | 105 |

| 3.1.3 Генераторы кода и библиотеки моделирования               | 109 |

| 3.2 Среда тестирования                                         | 111 |

| 3.2.1 Анализатор шаблонов тестовых программ                    | 112 |

| 3.2.2 Внутреннее представление шаблонов тестовых программ      | 113 |

| 3.2.3 Обработчик внутреннего представления                     | 115 |

| 3.2.4 Итератор последовательностей команд                      | 118 |

| 3.2.5 Распределитель регистров                                 | 120 |

| 3.2.6 Обработчик последовательностей команд                    | 121 |

| 3.2.7 Исполнитель последовательностей команд                   | 123 |

| 3.2.8 Генератор данных                                         | 124 |

| 3.2.9 Построитель встроенных проверок                          | 125 |

| 3.3 Расширяемость инструмента MicroTESK                        | 126 |

| 3.4 Выводы                                                     | 127 |

| Глава 4. Результаты практического применения                   | 128 |

| 4.1 Генератор тестовых программ для архитектуры MIPS64         | 128 |

| 4.1.1 Архитектура MIPS64                                       | 128 |

| 4.1.2 Спецификации архитектуры MIPS64                          | 129 |

| 4.1.3 Генерация тестовых программ для архитектуры MIPS64       | 131 |

| 4.2 Генератор тестовых программ для архитектуры ARMv8      | 132 |

|------------------------------------------------------------|-----|

| 4.2.1 Архитектура ARMv8                                    | 132 |

| 4.2.2 Спецификации архитектуры ARMv8                       | 133 |

| 4.2.3 Генерация тестовых программ для архитектуры ARMv8    | 138 |

| 4.2.4 Проверка корректности генерируемых тестовых программ | 139 |

| 4.3 Генератор тестовых программ для архитектуры PowerPC    | 140 |

| 4.3.1 Архитектура PowerPC                                  | 140 |

| 4.3.2 Спецификации архитектуры PowerPC                     | 140 |

| 4.3.3 Генерация тестовых программ для архитектуры PowerPC  | 141 |

| 4.4 Генератор тестовых программ для архитектуры RISC-V     | 142 |

| 4.4.1 Архитектура RISC-V                                   | 142 |

| 4.4.2 Спецификации архитектуры RISC-V                      | 142 |

| 4.4.3 Генерация тестовых программ для архитектуры RISC-V   | 145 |

| 4.5 Выводы                                                 | 146 |

| Заключение                                                 | 148 |

| Список литературы                                          | 149 |

| Приложения                                                 | 161 |

#### Введение

#### Актуальность темы

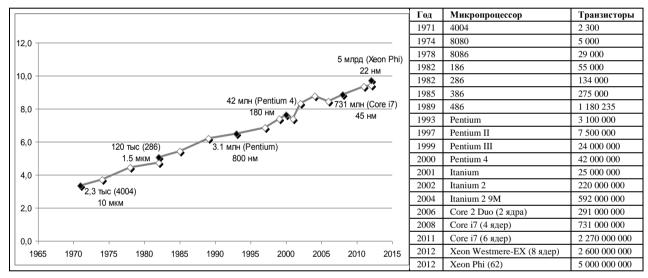

Микропроцессоры [16] лежат в основе большинства электронных устройств. В то время как другие компоненты отвечают за ввод и вывод данных, роль микропроцессора состоит в обработке этих данных: определяет, какие операции должны быть выполнены над данными контролирует процесс их выполнения. Микропроцессоры состоят из множества объединенных единый вычислительный транзисторов, В полупроводниковом кристалле. Число транзисторов увеличивается по закону Мура [17] и в настоящее время достигает нескольких миллиардов [18] (см. рисунок 1).

Рисунок 1. Рост числа транзисторов (на графике — десятичный логарифм) в микропроцессорах компании Intel

Высокая сложность современных микропроцессоров, вызванная оптимизацией производительности и энергопотребления, приводит ошибкам проектирования. Дальнейшее усложнение влечет за собой рост числа ошибок. Например, по данным на август 2008-го года в микропроцессоре Intel Pentium 4 было найдено 104 ошибки, из которых 43 не исправлено и их исправление не запланировано [19]. В то же время в микропроцессоре Intel Core i7-900 по данным на февраль 2015-го года обнаружено 167 ошибок, из которых исправлено только 16 и еще для 2 запланировано исправление [20]. Следует понимать, что в обоих случаях речь идет лишь об известных проблемах, в то время как реальное число ошибок может быть гораздо выше.

Цена ошибок в микропроцессорах очень высока. В отличие от дефектов в программах, которые устраняются сравнительно просто, микропроцессорах не могут быть исправлены и для их устранения потребуется повторный выпуск и замена микросхемы или целого блока. Например, в 1994-м продукции из-за ошибки В реализации **FDIV** году замена команды 475 микропроцессора Pentium обошлась компании Intel B миллионов долларов [21].

Обеспечение функциональной корректности микропроцессоров является фундаментальной проблемой, для решения которой применяется комплекс мер, известный как функциональная верификация. Она выполняется параллельно с задача заключается проектированием, и ee В проверке соответствия результатов, полученных на текущем этапе, заданным требованиям Верификация является трудоёмкой ограничениям. весьма задачей. некоторым оценкам, затраты на нее достигают 70-80% от общих затрат на инженеров-верификаторов проектирование, число примерно превосходит число инженеров-разработчиков [22]. С ростом сложности микропроцессоров ситуация только ухудшается — возможности методов верификации отстают от развития микропроцессоров; соответственно, проверка корректности (и без того являющаяся самым узким местом процесса проектирования) вовлекает в себя все большие объемы ресурсов. Таким образом, задача совершенствования методов и инструментов верификации имеет ключевое значение.

Наиболее часто применяемым на практике подходом к функциональной верификации микропроцессоров является имитационная верификация (simulation-based verification), также называемая тестированием. На системном уровне (т.е. на уровне устройства в целом) она осуществляется следующим образом: создаются тестовые программы на языке ассемблера; программы запускаются на проектной модели микропроцессора; в результате получаются трассы исполнения, содержащие информацию о событиях, которые

произошли в процессе исполнения программ; полученные трассы проверяются на корректность.

Создание тестовых программ осуществляется при помощи специальных программных инструментов, известных как генераторы тестовых программ. Они используют различные техники генерации для обеспечения максимальной полноты тестирования: от случайной генерации до нацеленной генерации, основанной на формальных методах. Ни одна ИЗ них не является универсальным решением для всех задач верификации, поэтому на практике применяется множество дополняющих друг друга техник. Общепринятым подходом является генерация на основе шаблонов тестовых программ, описывающих структурные и поведенческие свойства программ. Обработка тестового шаблона состоит в применении той или иной техники генерации для удовлетворения того или иного свойства.

Как правило, генераторы тестовых программ предназначены конкретных микропроцессорных архитектур и основаны на конкретных техниках генерации. Однако, так как микропроцессорные архитектуры и техники генерации эволюционируют, возникает задача расширения возможностей существующих генераторов. Трудность ее решения заключается в том, что знание об архитектуре микропроцессора зачастую неотделимо от реализации техник генерации. Поддержка новых архитектур и техник генерации требует существенных изменений в реализации генератора. Чтобы инженеры-верификаторы ЭТОГО избежать, вынуждены одновременно использовать несколько генераторов, каждый из которых решает какую-то отдельную задачу. При этом совместное использование различных техник генерации для решения общей задачи оказывается невозможным.

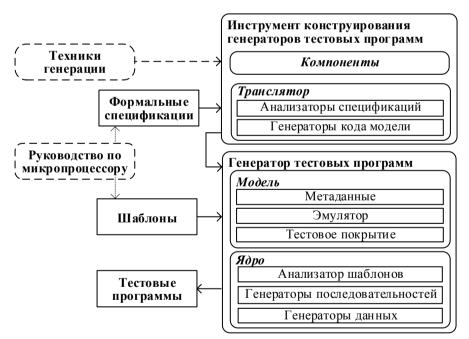

Таким образом, актуальной является разработки задача метода, позволяющего создавать ДЛЯ любых микропроцессорных архитектур генераторы тестовых программ, интегрирующие в себе разные техники генерации. Перспективным решением данной задачи видится автоматизированное конструирование генераторов тестовых программ на основе формальных спецификаций архитектуры микропроцессора. При этом формальные спецификации будут выступать в качестве источника знания об архитектуре тестируемого микропроцессора, используемого компонентами генератора, реализующими техники генерации. Генерация будет осуществляться на основе шаблонов, разработанных на специальном языке, позволяющем описывать свойства тестовых программ в терминах формальных спецификаций и задавать техники генерации, применяемые для удовлетворения этих свойств.

#### Цель и задачи работы

Цель работы — разработка метода автоматизации конструирования генераторов тестовых программ для микропроцессоров. Метод должен быть применимым к широкому спектру микропроцессорных архитектур. Генераторы должны создавать тестовые программы на языке ассемблера по шаблонам, описывающим структурные и поведенческие свойства этих программ. Генераторы должны реализовывать разные техники генерации и быть расширяемыми. Для достижения цели работы были поставлены следующие задачи:

- 1. Провести анализ существующих методов и средств генерации тестовых программ для микропроцессоров.

- 2. Разработать метод автоматизации конструирования генераторов тестовых программ для микропроцессоров на основе формальных спецификаций.

- 3. Разработать язык описания шаблонов тестовых программ, позволяющий описывать их структурные и поведенческие свойства.

- 4. Разработать архитектуру расширяемого генератора тестовых программ для микропроцессоров, позволяющую интегрировать разные техники генерации.

- 5. Разработать программный инструмент, реализующий предложенный метод автоматизации конструирования генераторов тестовых программ.

- 6. Оценить характеристики предложенного метода на основе опыта применения разработанного программного инструмента для

конструирования генераторов тестовых программ для нескольких микропроцессорных архитектур.

#### Научная новизна работы

Научной новизной обладают следующие результаты работы:

- 1. Метод автоматизации конструирования генераторов тестовых программ для микропроцессоров на основе формальных спецификаций.

- 2. Язык описания шаблонов тестовых программ, позволяющий описывать их структурные и поведенческие свойства.

- 3. Архитектура генератора тестовых программ для микропроцессоров, позволяющая интегрировать разные техники генерации.

#### Теоретическая и практическая значимость

В работе предложен метод автоматизации конструирования генераторов тестовых программ для микропроцессоров. В основе предложенного метода лежат архитектурно-независимые техники генерации, для применения которых к конкретной микропроцессорной архитектуре используется информация, полученная в результате анализа формальных спецификаций этой архитектуры. Результаты проведенного исследования могут послужить основой для разработки архитектурно-независимых техник генерации тестовых программ и создания программных инструментов, основанных на анализе формальных спецификаций. Кроме этого, эти результаты могут использоваться в исследовательских проектах и учебных курсах по проектированию и верификации микропроцессоров.

На основе предложенного метода разработан программный инструмент MicroTESK, позволяющий автоматизировать на основе формальных спецификаций конструирование генераторов тестовых программ ДЛЯ микропроцессоров. Разработанный инструмент был применен для создания генераторов тестовых программ для архитектур MIPS64, ARMv8, PowerPC и RISC-V. Генераторы тестовых программ для MIPS64 и ARMv8 используются в отечественных и зарубежных компаниях. Помимо этого, разработанный инструмент может быть использован для создания генераторов тестовых программ для широкого спектра других микропроцессорных архитектур.

#### Методология и методы исследования

Методологическую основу исследования составляют теория компиляторов, теория формальных языков, теория автоматов, теория множеств, теория графов, теория алгоритмов и математическая логика.

#### Положения, выносимые на защиту

- 1. Метод автоматизации конструирования генераторов тестовых программ для микропроцессоров на основе формальных спецификаций.

- 2. Язык описания шаблонов тестовых программ, позволяющий описывать их структурные и поведенческие свойства.

- 3. Архитектура генераторов тестовых программ для микропроцессоров, позволяющая интегрировать разные техники генерации и допускающая расширение множества поддерживаемых техник.

- 4. Программный инструмент, использующий предложенный метод для конструирования генераторов тестовых программ с предложенной архитектурой, осуществляющих генерацию на основе шаблонов на предложенном языке.

# Апробация работы

Основные положения работы обсуждались на следующих конференциях и семинарах:

- Международная конференция «Design Automation Conference», выставка University Booth (г. Остин, США, 2-7 июня 2013 г. и г. Сан-Франциско, США, 2-5 июня 2014 г.);

- Международная конференция «Design, Automation & Test in Europe»,

выставка University Booth (г. Гренобль, Франция, 18-22 марта 2013 г.;

г. Дрезден, Германия, 24-28 марта 2014 г.; г. Гренобль, Франция, 10-12 марта 2015 г.; г. Лозанна, Швейцария, 28-30 марта 2017 г.);

- Международный коллоквиум молодых исследователей в области программной инженерии «Spring/Summer Young Researchers' Colloquium on Software Engineering» (г. Пермь, 30-31 мая 2012 г. и д. Красновидово, 30 мая-1 июня 2016 г.);

- Международная конференция «A.P. Ershov Informatics Conference» (г. Москва, 27-29 июня 2017 г.);

- Открытая конференция ИСП РАН (г. Москва, 1-2 декабря 2016 г.);

- Международный симпозиум «IEEE East-West Design & Test Symposium» (г. Ереван, Армения, 14-17 октября 2016 г.);

- Всероссийская научно-техническая конференция «Проблемы разработки перспективных микро- и наноэлектронных систем» МЭС-2016 (г. Москва, 3-7 октября 2016 г.);

- Международная конференция «Новые информационные технологии в исследовании сложных структур» (г. Екатеринбург, 6-10 июня 2016 г.);

- Международная летняя школа молодых ученых «Новые информационные технологии в исследовании сложных структур» (г. Анапа, 8-12 июня 2015 г.);

- Научно-техническая конференция студентов, аспирантов и молодых специалистов НИУ ВШЭ им. Е.В. Арменского (г. Москва, 4 февраля 2015 г.);

- Совместный семинар ЗАО «МЦСТ» и ИСП РАН «Проблемы верификации микропроцессоров» (г. Москва, 10 апреля 2014 г.);

- Семинар Института системного программирования РАН (г. Москва, 2013, 2014 и 2016 гг.).

### Публикации

По теме диссертации автором опубликовано 15 работ, в том числе 7 научных статей [1–7] в рецензируемых журналах, входящих в перечень журналов, рекомендованных ВАК РФ. В работе [2] автором описывается архитектура инструмента MicroTESK. В статье [5] вклад автора заключается в

описании средств системной верификации микропроцессоров. В работах [6, 14] автору принадлежит описание концепции и архитектуры расширяемой среды генерации тестовых программ. В работах [7, 10, 11] вклад автора состоит в разработке средств моделирования подсистемы памяти и конструкций языка описания шаблонов тестовых программ, позволяющих создавать тесты на подсистему памяти. В работе [13] автором дается обзор существующих подходов и формулируются требования к системе хранения информации, используемой для построения тестов. В статье [15] автором описываются предлагаемый подход к моделированию архитектуры микропроцессора и концепция языка описания шаблонов тестовых программ.

#### Личный вклад

Все представленные в диссертации результаты получены лично автором.

#### Структура и объем диссертации

Работа состоит из введения, четырех глав, заключения, списка литературы (122 наименования) и одного приложения. Основной текст диссертации (без списка литературы и приложения) занимает 148 страниц.

#### Краткое содержание диссертации

Во введении обосновывается актуальность темы работы, определяются ее цели и задачи, раскрывается теоретическая и практическая значимость.

Первая глава содержит обзор подходов к функциональной верификации микропроцессоров. Основное внимание уделяется верификации при помощи тестовых программ. В главе рассматриваются сильные и слабые стороны распространенных техник генерации тестовых программ, области ИХ применения и варианты их совместного использования. Также делается сравнительный возможностей существующих инструментов, анализ реализующих эти техники. На основе данного анализа делается вывод об отсутствии генератора тестовых программ, который был бы применим для широкого спектра микропроцессорных архитектур И позволил бы интегрировать основные применяемые на практике техники генерации, и выдвигается тезис об актуальности задачи его создания.

Во второй главе предлагается метод автоматизации конструирования генераторов тестовых программ для микропроцессоров на основе формальных спецификаций их архитектуры. Данный метод предполагает, что информация, формальных спецификаций, будет извлеченная ИЗ использоваться для обеспечения целенаправленности тестирования И контроля состояния микропроцессора в процессе генерации. Построение тестовых программ будет шаблонов, осуществляться на основе разработанных на специальном расширяемом языке, позволяющем описывать их структурные и поведенческие свойства. Расширяемая архитектура генераторов позволит интегрировать разные техники генерации. Глава состоит из трех разделов, в которых описывается предлагаемый метод автоматизации конструирования генераторов тестовых программ, язык описания шаблонов тестовых программ и архитектура конструируемых генераторов тестовых соответственно.

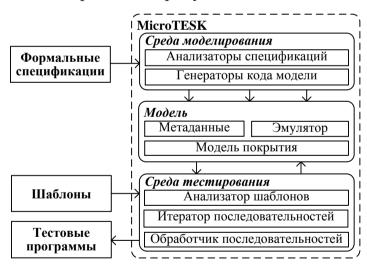

В третьей главе описывается реализация предложенного метода автоматизации конструирования генераторов тестовых программ. Метод нашел свое воплощение инструменте открытым исходным кодом MicroTESK (Microprocessor **TEsting** and Specification Kit) 2.0, версии разработанном на языке Java. Данный инструмент на основе формальных спецификаций конструирует генераторы тестовых программ, состоящие из модели микропроцессора и архитектурно-независимого ядра. Глава состоит из двух разделов, в которых описывается реализации инструмента MicroTESK и реализация архитектурно-независимого ядра генераторов тестовых программ соответственно.

В четвертой главе описываются результаты применения предложенного метода автоматизации конструирования генераторов тестовых программ для микропроцессоров MIPS64, ARMv8, PowerPC и RISC-V. В главе оценивается трудоемкость создания генераторов с применением предложенного метода и приводится сравнение с результатами применения других аналогичных

методов. Также в главе обосновывается применимость предложенного метода для конструирования генераторов тестовых программ для микропроцессорных архитектур промышленного масштаба.

В заключении перечисляются основные результаты работы.

# Глава 1. Генерация тестовых программ для микропроцессоров

Данная глава содержит обзор техник и инструментов, применяемых для функциональной верификации генерации тестовых программ ДЛЯ микропроцессоров. В начале главы рассказывается об области применения генераторов тестовых программ, а затем делается сравнительный анализ существующих техник И инструментов. Ha основе данного формулируется основные требования к методу автоматизации конструирования генераторов тестовых программ, предлагаемому в данной работе.

#### 1.1 Проектирование микропроцессоров

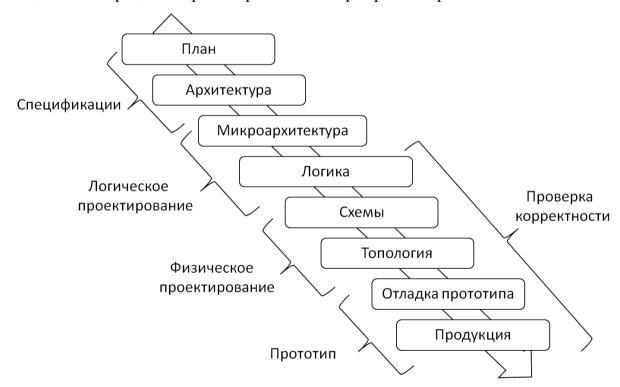

Проектирование микропроцессора — сложный процесс, включающий в себя нескольких этапов [16, 25, 26], на каждом из которых создается описание микропроцессора на определенном уровне абстракции. На рисунке 2 показана общая схема процесса проектирования микропроцессора.

Рисунок 2. Процесс проектирования микропроцессора

Проектирование микропроцессора начинается с составления детального плана (технического задания), в котором описывается концепция проектируемого устройства, целевая рыночная ниша и основные характеристики (такие как цена, производительность и энергопотребление). Также определяется на основе каких предыдущих разработок будет создан микропроцессор и какое программное обеспечение будет на нем запускаться. Помимо этого делается оценка времени и ресурсов, отведенных на проектирование, составляется график работ и выбирается общая методология проектирования.

На этапе проектирования архитектуры определяется, какие команды поддерживаться микропроцессором. Ha ЭТОМ этапе уточняются требования и создается спецификация архитектуры. Помимо документов требований и спецификаций архитектуры результатом данного этапа является (симулятор), программный эмулятор позволяющий интерпретировать программы, написанные ДЛЯ целевого микропроцессора. Он может кросс-разработки обеспечения использоваться для программного или выступать в качестве эталонной модели.

После архитектуры проектируется микроархитектура. Она описывает функциональные модули микропроцессора, их взаимодействие и разделение задач между ними. На этом этапе определяются такие характеристики, как организация конвейера команд и иерархии памяти, способ реализации многопоточности Обычно И Т.Д. результатом проектирования микроархитектуры являются диаграммы взаимодействия между модулями и спецификации, описывающие различные алгоритмы. Кроме того на этапах проектирования архитектуры И микроархитектуры осуществляется моделирование. Для этого применяются следующие средства: (1) языки программирования общего назначения, (2) языки системного проектирования (SLDL, System-Level Design Languages) и (3) языки описания архитектуры (ADL, Architecture Description Languages) [27, 28, 29]. Примеры языков указанных типов представлены в таблице 1. С их помощью создаются модели для проведения различных экспериментов (например, программные эмуляторы или формальные модели), а также средства разработки для проектируемой архитектуры (компиляторы, дизассемблеры, и т.д.).

Таблица 1. Языки, используемые при проектировании микропроцессоров

| Тип языка                                | Примеры                          |

|------------------------------------------|----------------------------------|

| Языки программирования общего назначения | C, C++, Perl, Python             |

| Языки описания архитектуры (ADL)         | LISA, EXPRESSION, ISDL, nML      |

| Языки системного проектирования (SLDL)   | SystemC, SystemVerilog, Bluespec |

| Языки описания аппаратуры (HDL)          | Verilog, VHDL                    |

На следующем этапе при помощи языков описания аппаратуры (HDL, Hardware Description Languages) описывается логическая структура микропроцессора. Результатом данного этапа является модель *уровня* регистровых передач (RTL, Register Transfer Level), называемая также HDLмоделью или HDL-описанием, которая с потактовой точностью определяет пересылки данных, возникающие при работе устройства. На этапе разработки HDL-модели часто прибегают к прототипированию (prototyping) [30]. Оно предполагает создание функционально идентичной реализации, выполненной с использованием программируемых логических интегральных схем (ПЛИС), с целью проведения различных экспериментов.

После этого на основе HDL-модели строится функционально ей эквивалентная *схема* из логических вентилей в заданном технологическом базисе. Процесс построения данной схемы осуществляется средствами *систем* автоматизированного проектирования (САПР) и называется логическим синтезом.

осуществляется построение топологии, которая описывает размещение транзисторов и проводников в слоях материала, их которого изготовляется схема на кристалле. Этот этап называется физическим синтезом и он, также как и логический синтез, автоматизирован средствами САПР. В результате получается представление (как правило, основанное фотошаблонах), которое затем используется при производстве интегральных схем.

По завершению физического проектирования осуществляется *выпуск* (*tape-out*) первого *опытного образца (first silicon*) интегральной схемы. Данный образец проходит несколько циклов отладки, в процессе которых выявляются и

исправляются ошибки, перед тем как, созданный микропроцессор может быть выпущен на рынок.

#### 1.2 Функциональная верификация микропроцессоров

Параллельно с процессом проектирования осуществляется контроль корректности полученных результатов. Для обеспечения функциональной корректности микропроцессоров применяется комплекс мер, известный как функциональная верификация. Прежде всего, ЭТИ меры нацелены обнаружение и исправление ошибок, допущенных в процессе проектирования. Хотя функциональная верификация присутствует на всех этапах, особенно она актуальна при создании HDL-модели, поскольку функциональность, описанная впоследствии не изменяется [26]. Верификация на ЭТОМ этапе, осуществляться как на уровне отдельных модулей микропроцессора (модульная верификация), так и для устройства в целом (системная верификация).

Существуют два основных подхода к функциональной верификации: (1) имитационная верификация (simulation-based verification), также называемая (2) формальная верификация (formal тестированием, И method-based verification) [31]. Первый заключается в проверке корректности реакции проектируемого устройства, работа которого имитируется при помощи программного или аппаратного эмулятора, на тестовые воздействия. Второй основан на построении математической (формальной) модели и проверке выполнимости ее свойств. Формальная верификация позволяет осуществить исчерпывающую проверку всех возможных вариантов поведения, заданных моделью. Однако она имеет ряд ограничений (высокая трудоемкость и вычислительная сложность, а также трудности формализации), которые затрудняют ее использование в промышленных проектах. По этой причине на практике основной акцент делается на тестирование [32].

Тестирование микропроцессоров на системном уровне осуществляется путем генерации *тестовых программ* на языке ассемблера, которые представляют собой последовательности команд (инструкций) микропроцессора, и анализа результатов их выполнения с целью убедиться, что

их поведение соответствует спецификации. Такой подход видится наиболее функциональность естественным, Т.К. система команд определяет микропроцессора и является единственным доступным интерфейсом, через который пользователи могут с ним взаимодействовать. Верификация при помощи тестовых программ применима на всех этапах проектирования, начиная с момента создания программного эмулятора, но на каждом этапе имеет свои особенности, связанные со скоростью выполнения программ и уровнем детализации полученных результатов. В таблице 2 показаны примерная скорость выполнения тестов и уровень детализации результатов на различных прототипах [33]. Обычно тестирование начинается с HDL-модели и продолжается до выпуска продукции.

Таблица 2. Скорость выполнения тестов и уровень детализации результатов на различных прототипах

| Объект тестирования             | Скорость выполнения (инстр./сек.) | Уровень детализации |

|---------------------------------|-----------------------------------|---------------------|

| HDL-эмулятор                    | $10^{3}$                          | Очень высокая       |

| Эталонный эмулятор на С/С++     | 3 * 10 <sup>6</sup>               | Высокая             |

| ПЛИС-прототип                   | 10 <sup>7</sup>                   | Средняя             |

| Опытный образец микропроцессора | $10^8 - 10^9$                     | Очень низкая        |

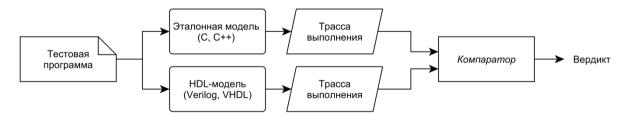

Существуют два основных подхода к функциональной верификации микропроцессоров при помощи тестовых программ: (1) сравнение *трасс выполнения* с эталонными трассами и (2) использование *встроенных проверок* (*self-checks*).

Рисунок 3. Тестирование посредством сравнения трасс

В первом случае (см. рисунок 3) при выполнении программы на HDL-модели или другой программной модели создается трасса выполнения, фиксирующая события, которые происходят в микропроцессоре. Полученная трасса сравнивается с эталонной трассой, полученной в результате выполнения той же программы на эталонной модели (reference model). Для сравнения трасс используются специальные программы, называемые компараторами.

Эталонная модель создается независимо от HDL-модели на языке высокого уровня (например, С или С++) и является более абстрактной. Часто в качестве эталонной модели выступает эмулятор уровня инструкций (instruction-level simulator), разработанный на стадии архитектурного проектирования. Более абстрактная модель, как правило, содержит меньшее количество ошибок, а тот факт, что она разрабатывается независимо, уменьшает вероятность повторения ошибок, допущенных при создании HDL-модели. Данный подход позволяет универсальным образом осуществлять проверку корректности поведения микропроцессора при выполнении различных тестовых программ. Таким образом, отпадает необходимость реализовывать проверки для отдельных тестов. К недостаткам подхода, можно отнести то, что трассы, полученные при помощи упрощенной эталонной модели, могут не отражать все события, которые происходят в HDL-модели (и реальном процессоре). Это приводит к трудностям при сопоставлении трасс.

Второй подход предполагает, что код тестовой программы содержит проверки, которые необходимо осуществить в процессе ее выполнения. Такие программы можно выполнять не только на HDL-моделях, но и на аппаратных ускорителях, ПЛИС-прототипах и экспериментальных образцах микросхем (post-silicon verification). Это позволяет повысить производительность, так как время выполнения программы на аппаратных эмуляторах существенно меньше, чем на программных. Однако при таком подходе снижается точность проверки, так как множество событий, которые может фиксировать тестовая программа, ограничено.

Решение о завершении верификации принимается на основе набора критериев, который включает в себя следующее [34]:

- выполнение плана верификации;

- отсутствие ошибок при прогоне регрессионных тестов;

- отсутствие ошибок на  $10^5$  псевдослучайных тестов для каждого из имеющихся тестовых шаблонов;

- достижение заданного уровня покрытия HDL-кода и функционального

покрытия;

- отсутствие изменений в HDL-коде в течение длительного времени (3-4 недели);

- отсутствие новых ошибок в течение определенного времени (2-3 недели);

- истечение отведенного согласно плану времени на разработку и верификацию.

Особого внимания заслуживают критерии, основанные на достижении требуемого уровня покрытия. Достигнутый уровень покрытия оценивается при помощи тестового покрытия [35]. Они метрик представляют выбранной количественные характеристики полноты покрытия модели тестового покрытия, которая описывается как конечный набор тестовых ситуаций. Числовое значение метрики покрытия представлено как отношение числа достигнутых при выполнении теста ситуаций к общему числу ситуаций в модели. Выделяют два типа моделей покрытия: (1) основанные на реализации и (2) основанные на функциональных требованиях.

В моделях первого типа тестовые ситуации связаны непосредственно с кодом HDL-модели или с производными от нее структурами. Т.е. метрики покрытия на основе реализации позволяют оценить, в какой мере код HDL-модели был задействован при выполнении набора тестов. Примерами таких метрик являются: покрытие строк кода (line coverage), покрытие операторов (statement coverage), покрытие переходов управления (branch coverage), а также покрытие состояний, дуг и путей (state, arc, transition coverage) конечных автоматов [36]. Большинство современных САПР предоставляют инструментарий для сбора и анализа данных о достигнутом покрытии реализации.

В моделях второго типа, известных как *модели функционального покрытия*, тестовые ситуации задаются в терминах абстракций микроархитектуры или архитектуры микропроцессора, а также абстракций более высокого уровня. Такие модели создаются на основе спецификаций *функциональных требований* к микропроцессору различного уровня. Они могут

создаваться вручную или посредством анализа формальных спецификаций [37], разработанных в процессе проектирования архитектуры и микроархитектуры.

Важно отметить, что ни одна из метрик тестового покрытия, взятая в отдельности не даёт ответа на вопрос о полноте набора тестов. Поэтому на практике используются комбинации различных метрик, основанных как на реализации, так и на функциональных требованиях.

Для генерации тестов, предназначенных для достижения требуемого уровня покрытия для выбранных метрик, применяются разнообразные техники автоматической генерации тестовых программ. Инструменты, при помощи которых осуществляется генерация, известны как генераторы тестовых программ (TPG, test program generators) или генераторы потока команд (ISG, generators). instruction stream Помимо генерации тестовых программ практикуется ручная разработка И использование существующего программного обеспечения [33], однако применимость этих подходов разработка ограничена. Ручная обладает высокой трудоемкостью. существующее программное обеспечение не гарантий дает полноты функционально покрытия. Кроме того его запуск на HDL-эмуляторе может занимать много времени. Поэтому основной акцент делается на генерацию.

## 1.3 Техники генерации тестовых программ

Большинство современных генераторов тестовых программ в той или иной степени полагаются на *случайную генерацию* [38]. Однако применяемые техники генерации могут существенно отличаться степенью *нацеленности*. Под нацеленностью следует понимать ориентированность на покрытие конкретных тестовых ситуаций или классов тестовых ситуаций. Следует заметить, что т.к. генерация тестовых программ предполагает повторяемость результатов, алгоритмы случайной генерации, как правило, основаны на детерминированных генераторах псевдослучайных чисел.

В простейшем случае команды и их входные значения выбираются случайным образом [39]. Инструмент, решающий подобную задачу, можно разработать достаточно быстро, и он позволит сгенерировать набор тестов,

обеспечивающих базовый уровень покрытия. К сожалению, такой подход не является систематическим и не позволит достичь полного покрытия. Подобные инструменты не располагают сведениями о семантике команд и особенностях реализации микроархитектуры, поэтому не гарантируют достижения всех интересных с точки зрения тестирования ситуаций, а также корректности построенной программы (отсутствие зацикливаний, переходов на секцию данных, нарушений инвариантов команд, и т.д.).

Первый шаг в направлении повышения нацеленности случайных тестов – ограничение области допустимых значений для случайного выбора присвоение весов выбираем вариантам [40]. Такой подход предполагает описание задач генерации в виде шаблонов, которые задают списки команд для выбора (в том числе иерархические), веса отдельных элементов и области аргументов. Это более значений ИХ входных позволит тщательно протестировать отдельные команды или классы команд. Веса и области значений подбираются на основе полученных значений метрик тестового покрытия.

Следующий шаг сторону улучшения покрытия предполагает использование техник комбинаторной генерации [41]. Такой подход позволит нацелить генератор на тестирование ситуаций, связанных с совместным конвейере. выполнением команд на Суть подхода заключается систематическом переборе коротких последовательностей команд (включая зависимости между ними). Помимо этого можно получать входные аргументы команд путем перебора данных из некоторого предопределенного набора. Это позволит достичь лучшего покрытия пограничных случаев (corner cases). Путем совместного использования техник случайной и комбинаторной генерации можно построить более сложные тесты, которые помогут покрыть многие маловероятные и трудновообразимые ситуации в работе микропроцессора.

Для проверки поведения микропроцессора в конкретных ситуациях часто прибегают к *детерминированной эмуляции (deterministic simulation)* [42]. Идея заключается в создании тестовых программ с детерминированным поведением,

проверки. Изначально включающих встроенные такие программы разрабатывались вручную, что делало их создание крайне трудоемкой задачей. Автоматическая генерация таких программ предполагает исполнение команд в процессе генерации и использование полученных результатов для создания Исполнение команд в процессе генерации также позволяет гарантировать корректность построенных программ. При данном подходе программы стоятся по шаблонам, которые описывают тестовый сценарий. Исполнение команд генератор осуществляет самостоятельно или использует для этого внешние эталонные модели. Построенные таким образом тесты можно считать полностью нацеленными. Основным недостатком данного подхода остается трудоемкость создания тестов, которая сопоставима с ручной разработкой. Как и при ручной разработке, чтобы создать код, покрывающий нетривиальные ситуации в работе микропроцессора, от разработчика требуется глубокое знание особенностей микроархитектуры. Кроме того, есть риск, что некоторые ситуации будут пропущены. С целью улучшения покрытия и уменьшения трудозатрат шаблоны могут использовать рандомизацию или комбинаторный перебор. Например, построение тестовых программ может осуществляться путем перебора разнообразных графов потока управления (структур переходов), описанных в шаблоне, и маршрутов в них (трасс выполнения) [43].

Построение нацеленных тестов можно упростить при помощи генерации на основе ограничений [44]. При таком подходе в шаблонах указываются ограничения, которым должны удовлетворять операнды команд. Ограничения соответствуют тестовым ситуациям, основанным на особенностях реализации микроархитектуры или на функциональных требованиях. В процессе обработки шаблона генератор, используя некоторый механизм разрешения ограничений, который зависит от их типа, строит случайные значения, удовлетворяющие заданным ограничениям. Использование ограничений позволяет значительно сократить трудозатраты, связанные с подбором значений операндов, требуемых для покрытия тестовых ситуаций. Однако, т.к. тестовые шаблоны по-прежнему

разрабатываются вручную, остается риск упустить важную для тестирования ситуацию.

Систематическое тестирование может быть обеспечено путем создания формальных моделей тестируемого микропроцессора [45] и применения к ним техник проверки моделей для построения тестов, охватывающих все пространство состояний. Такой подход называют генерацией на основе моделей. Т.к. современные микропроцессоры имеют огромное количество состояний и переходов между ними, у этого метода будут высокие вычислительные затраты. Для их сокращения можно использовать тестовые шаблоны, которые будут задавать направление тестирования. К недостаткам данного подхода относятся высокая трудоемкость его реализации (пока ведутся исследования, но нет промышленных инструментов), а также трудности создания формальных моделей.

Таблица 3. Техники генерации и требуем ые ими входные данные

| Техника генерации                                               | Входные данные                                                                                                             |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Случайная генерация                                             | Ассемблерный формат команд;<br>Тестовые шаблоны (списки команд, веса)                                                      |

| Комбинаторная генерация                                         | Все выше перечисленное;<br>Тестовые шаблоны (правила комбинирования)                                                       |

| Генерация детерминированных тестов со<br>встроенными проверками | Все выше перечисленное;<br>Тестовые шаблоны (описание тестовых сценариев);<br>Семантика команд (эталонная модель)          |

| Генерация на основе ограничений                                 | Все выше перечисленное;<br>Тестовые шаблоны (задание ограничений);<br>Модели покрытия (наборы ограничений) различного типа |

| Генерация на основе моделей                                     | Все выше перечисленное;<br>Формальные модели микропроцессора                                                               |

Как можно заметить, перечисленным техникам требуется разное количество входных данных. В таблице 3 приводится список техник и требуемых для них входных данных в порядке увеличения их количества. Реализации перечисленных техник в различных инструментах генерации могут отличаться. Отдельный инструмент может поддерживать один или несколько техник. Особенности реализации техник в конкретных инструментах будут рассмотрены далее.

#### 1.4 Инструменты генерации тестовых программ

#### 1.4.1 Инструменты НИИСИ РАН

B НИИСИ PAH разрабатывается система INTEG [40, 46], MIPS64 [47]. предназначенная ДЛЯ тестирования микропроцессоров Используемый ею подход к тестированию называется стохастическим. Он предполагает генерацию тестовых программ по заданному шаблону с параметризированным случайным выбором команд и их аргументов. После этого осуществляется исполнение сгенерированных программ на HDL-модели и на эталонной модели, в качестве которой выступает программный эмулятор VMIPS [48], и сравнение полученных результатов.

Генератор тестовых программ системы INTEG поддерживает случайные комбинаторные техники генерации. Тестовые шаблоны ДЛЯ него разрабатываются на специализированном языке, конструкции основаны на синтаксисе языка С. Система предоставляет графический интерфейс, который упрощает ИХ разработку. Шаблоны задают последовательность фрагментов кода в тестовой программе, состав входящих в них команд и аргументы этих команд. Все параметры, оставленные свободными, генератор выбирает случайно, в соответствии с заданными для вероятностями. Основные возможности, предоставляемые описания тестовых шаблонов, включают: (1) задание областей памяти для кода и для данных; (2) описание последовательностей команд (в том числе конструкции для описания циклов); (3) выбор команд; (4) выбор регистров, используемых в качестве аргументов команд; (5) задание значений аргументов (6) задание адресов данных И адресов передачи команд: управления; (7) описание правил генерации случайных значений; (8) создание макросов для повторного использования шаблонного кода. При разработке тестовых шаблонов для системы INTEG руководствуются планом тестирования и метриками покрытия код HDL-модели. Для устранения пробелов в покрытии изменяются настройки шаблонов, такие как степень случайности выбора, область допустимых значений, т.д.

В процессе генерации система INTEG отслеживает состояние микропроцессора, используя упрощенный подход. При таком подходе исполнение команд на эмуляторе не осуществляется, а значение регистров в некоторой точке выполнения считается известным или неопределенным. При необходимости генератор обновляет значения регистров и обеспечивает защиту от записи в регистры, часто используемые для чтения.

Система INTEG предоставляет достаточно мощный и удобный инструментарий для создания случайных тестов. Средства разработки тестовых шаблонов, генерации тестовых программ, выполнения тестирования, а также анализа его результатов интегрированы в единую систему. Однако данная система имеет ряд ограничений:

- Поддерживаются только случайная и комбинаторная генерация. Остается неясно, какой уровень функционального покрытия можно обеспечить этими методами и насколько сложно разработать шаблоны, удовлетворяющие требованиям по тестовому покрытию.

- Не предусмотрено добавление пользовательских техник генерации и пользовательских конструкций в язык описания тестовых шаблонов.

- В процессе генерации построенные команды не исполняются на эталонном эмуляторе. Таким образом, генератор не может отслеживать состояния микропроцессора в любой точке выполнения тестовой программы. Эта информация необходима для контроля корректности сгенерированных программ и создания встроенных проверок. Кроме того она требуется техникам генерации, основанным на разрешении ограничений. Таким образом, реализация перечисленных возможностей столкнется со значительными трудностями.

- Поддерживается только архитектура MIPS64. В работе [46] есть упоминание о возможности настройки под другие архитектуры. Однако неясно, каким образом такая настройка будет осуществляться и каких трудозатрат она потребует.

#### 1.4.2 Инструменты ARM

#### Инструменты RIS

В компании ARM [49] разработано семейство инструментов генерации тестовых программ, получившее название RIS (Random Instruction Sequence) [50, 51]. Это узкоспециализированные инструменты, предназначенные ДЛЯ решения различных задач тестирования микропроцессоров с архитектурой ARM. Решаемые ими задачи включают тестирование таких механизмов, как многоядерность [52] и управление памятью [53]. Настройка инструментов RIS осуществляется при помощи конфигурационных файлов, которые задают используемые команды, их веса, ограничения на их операнды, способы размещения кода и данных в памяти, а также цепочки команд, решающих специальные задачи (вытеснение данных из кэш-памяти и т.п.). Инструменты RIS, описанные в работах [52] и [53], не используют эталонные модели и не осуществляют исполнение команд в процессе генерации. В тех случаях, когда требуются встроенные проверки, тесты выполняются дважды И полученные результаты сравниваются (применимо только для детерминированных результатов). Такой подход упрощает разработку инструмента и делает возможным его использование непосредственно на ПЛИС-прототипе или экспериментальном микропроцессора. К сожалению, доступная информация об инструментах RIS не позволяет в полной мере оценить их функциональные возможности. Из того, что известно можно сделать вывод, что основным ограничением инструментов является то, что они жестко привязаны к архитектуре ARM и RIS ориентированы на решение конкретных задач. Поддержка других архитектур и техник генерации в них не предусмотрена.

#### Инструмент RAVEN

Другим инструментом, используемым в компании ARM, является RAVEN (Random Architecture Verification Machine) [54, 55, 56], разработанный в компании Obsidian Software, поглощенной ARM в 2011 году. Это

универсальное средство, применимое для широкого спектра архитектур, в котором ядро, реализующее логику генерации, отделено от конфигурации для конкретной архитектуры. RAVEN позволяет создавать как случайные, так и нацеленные тесты. В процессе работы инструмент отслеживает состояние микропроцессора путем исполнения построенных программ на внешней эталонной модели. Это позволяет гарантировать корректность построенных программ и использовать информацию о текущем состоянии микропроцессора для генерации тестов.

Конфигурация тестируемого микропроцессора задается в виде XMLфайлов. Данные файлы содержат следующую информацию об архитектуре тестируемого микропроцессора: (1) перечень поддерживаемых команд и их групп, организованный в виде дерева; (2) сигнатуры команд (ассемблерный кодировка); (3) операнды синтаксис, двоичная команд, свойства, используемые ими режимы адресации и правила их группировки; (4) семантика команд, представленная в виде формул; (5) ресурсы микропроцессора, к которым обращаются команды. Кроме того там также описываются специальные условия такие, как исключения, ситуации в работе конвейера инструкций и подсистемы памяти. Эти описания используются генератором для построения тестовых программ.

Другой важный аспект конфигурации — это внешняя эталонная модель, используемая генератором для отслеживания состояния микропроцессора. Она интегрируется в ядро инструмента при помощи специальных библиотек на языке С++. Как правило, модель разрабатывают производители микропроцессора, а интеграцию осуществляют разработчики инструмента. Это требует скоординированных совместных усилий т.к. для успешной интеграции необходимо, чтобы модель удовлетворяла требованиям, предъявляемым инструментом.

Задачи тестирования описываются при помощи шаблонов, которые разрабатывается вручную или создаются при помощи графического интерфейса. В шаблонах задаются используемые команды, вероятности их

появления, правила генерации входных значений, целевые тестовые ситуации т.д. Тестовые шаблоны разрабатываются в соответствии с таблицами тестового покрытия, которые формулируют цели тестирования. На основе метрик покрытия, полученных в результате выполнения построенных тестов, в набор шаблонов вносятся изменения до тех пор, пока требуемый уровень покрытия не будет достигнут.

Тестовые ситуации описываются в виде правил, основанных на ограничениях и различных эвристиках, которые хранятся в специальной базе знаний. Набор правил может пополняться. Это позволяет накапливать знания, используемые для построения тестов, и повторно применять их для тестирования других микропроцессоров.

Список тестовых ситуаций, покрытие которых может быть обеспечено при помощи инструмента RAVEN включает: (1) комбинации следующих друг за другом команд; (2) ситуации в работе операций с плавающей точкой; (3) исключения в работе команд; (4) конвейерные конфликты; (5) различные сценарии обработки запросов к иерархии памяти; (6) ситуации, связанные с совместным использованием памяти несколькими ядрами многоядерного микропроцессора.

К сожалению, информации об инструменте RAVEN, имеющаяся в открытом доступе, недостаточно подробна. Остается неясно, какой уровень нацеленности он позволяет достичь, насколько трудоемко писание тестовых ситуаций и предусматривается ли поддержка новых типов тестовых ситуаций. Также к недостаткам инструмента можно отнести то, что описание микропроцессора, используемое для генерации тестов, и эталонная модель являются дублирующимися представлениями одного и того же знания. Это усложняет поддержку особенно инструмента, если эти представления разрабатываются разными командами.

#### 1.4.3 Инструменты IBM Research

В IBM Research разрабатывается несколько инструментов генерации тестовых программ, которые имеют различное назначение и используются в

различных промышленных проектах. Изначально эти инструменты создавались для верификации микропроцессоров семейства PowerPC, а в дальнейшем применялись и для других архитектур (таких, как ARM и х86).

#### Инструмент Genesys-Pro

В настоящее время основным средством генерации тестовых программ, используемым в IBM, является Genesys-Pro [32]. Это универсальный инструмент, позволяющий создавать случайные и нацеленные тесты для различных типов микропроцессоров. Данный инструмент разделен на *ядро*, которое реализует методы генерации, применимые для любых архитектур, и *модель*, которая содержит всю информацию о тестируемом микропроцессоре. Задачи тестирования формулируются при помощи *тестовых шаблонов*. Стенерированные команды исполняются на внешнем программном эмуляторе с целью отслеживания состояния микропроцессора и контроля корректности построенной программы.

Инструмент Genesys-Pro включает В себя специальную среду моделирования, позволяющую создавать модели микропроцессоров на основе набора высокоуровневых блоков. Модели содержат информацию двух видов: (1) декларативное описание микропроцессора, которое включает в себя команды, ресурсы (регистры, память) и некоторые механизмы (например, трансляция адресов) и (2) тестовое знание для данного микропроцессора, которое представляет собой набор эвристик, позволяющих повысить уровень покрытия. Семантика команд описывается в виде ограничений на их входные аргументы. Описание команд также включает их сигнатуры, используемые ими ресурсы, типы данных аргументов и допустимые входные значения. Команды могут объединяться в группы. Среда моделирования имеет некоторые ограничения, не позволяющие описывать семантику некоторых типов команд. В частности для инструкций арифметики с плавающей точкой и команд доступа к памяти используются дополнительные инструменты, о которых будет рассказано в следующих разделах. Кроме того семантику некоторых сложных команд приходится описывать на языке С++.

Шаблоны языке [57], создаются на специализированном предоставляющем конструкции для описания последовательностей команд, распределений вероятностей и ограничений. Последовательности команд могут строиться при помощи техник случайной и комбинаторной генерации. Также язык предоставляет средства для описания последовательностей команд, которые будут выполняться в разных потоках (или разных ядрах). Входные аргументы команд генерируются случайным образом заданной (c вероятностью) или путем решения ограничений. Ограничения, задающие те или иные аспекты поведения инструкций, берутся из модели. Кроме этого существуют универсальные ограничения, которые ОНЖОМ следующие типы: (1) ограничения на выравнивание адресов; (2) зависимости по ресурсам для команд; (3) события, связанные с работой подсистемы памяти (промахи и попадания в различные буферы). Ограничения могут быть обязательными (hard) и необязательными (soft). Первые имеют более высокий вес при решении систем ограничений и, как правило, основаны на семантике команд. Вторые могут быть проигнорированы, если система ограничений не имеет решения, и обычно основаны на тестовом знании. Для ограничений можно задавать вероятности, с которыми они должны быть применены для выбранных команд. Также язык описания тестовых шаблонов поддерживает условную генерацию. Т.е. можно задавать пред- и постусловия, которые должны выполняться для того, чтобы фрагмент кода был добавлен в тестовую программу.

Генерация программ включает следующие тестовых стадии: (1) построение последовательностей команд; (2) решение ограничений (или генерация случайных значений) для каждой из команд; (3) исполнение команд на эталонной модели. В случае если не удается решить ограничения, инструмент может вносить коррективы В последовательность команд (добавлять дополнительные команд, повторно генерировать предыдущие команд).

Инструмент Genesys-Pro позволяет достичь достаточно высокого уровня нацеленности. Степень случайности тестов задается тестовыми шаблонами, которые разрабатываются в соответствии с планом верификации. Решение относительно полноты набора тестовых шаблонов принимается на основе метрик покрытия, основанных на реализации и функциональных требованиях.

К недостаткам Genesys-Pro можно отнести ограничения среды моделирования, которые требуют использования дополнительных средств для моделирования инструкций арифметики с плавающей точкой и доступа к памяти. Другим слабым местом является использование внешней эталонной модели для эмуляции исполнения команд. Это требует дополнительных трудозатрат на интеграцию и поддержку данной модели. Также непонятно насколько расширяемым является инструмент (возможность добавления новых техник генерации).

#### Инструмент FPGen

Для верификации модулей арифметики с плавающей точкой IBM Research был разработан инструмент FPGen [58]. Этот инструмент расширяет Genesys-Pro средствами генерации тестовых данных для покрытия всевозможных ситуаций в работе операций с плавающей точкой [59] (требования определены в стандарте IEEE 754 [60]).

Инструмент FPGen генерирует значения входных аргументов команд, разрешая специализированные ограничения. Ограничения определяют значения отдельных входных аргументов, отношения между значениями входных аргументов, результат промежуточных вычислений или конечный результат выполнения команды. Для описания ограничений используется язык XML. Генератор FPGen не привязан к какой-либо конкретной архитектуре, он генерирует наборы данных, которые сохраняются в специальном формате [60]. Эти данные используются Genesys-Pro при генерации тестовых программ, использующих операции арифметики с плавающей точкой. В процессе генерации Genesys-Pro комбинирует результаты решения ограничений, которые он разрешает самостоятельно и которые он разрешает при помощи FPGen.

#### **Инструмент DeepTrans**

Еще одно известное расширение Genesys-Pro – это инструмент DeepTrans [62], предназначенный для тестирования механизмов трансляции адресов. Этот инструмент использует спецификации подсистемы памяти, разработанные на специализированном языке моделирования. Данный язык позволяет представить процесс преобразования адреса В виде ориентированного ациклического графа, вершины которого соответствуют стадиям процесса, а дуги — переходам между стадиями. Множество путей от истока до стока задает конкретные варианты преобразования адреса и соответствует тестовым ситуациям. Тестовые ситуации представляются в виде ограничений, на которые можно ссылаться из тестовых шаблонов. За обработку шаблонов отвечает инструмент Genesys-Pro, который разрешает ограничения и трансформирует результаты в последовательности команд. К достоинствам DeepTrans следует отнести развитый язык моделирования механизмов трансляции. Он позволяет достаточно быстро осуществить настройку инструмента для тестирования механизмов трансляции адресов произвольного микропроцессора. Известный недостаток состоит в том, что не поддерживается автоматическое извлечение зависимостей между командами (конфликтов использования устройств); их приходится дополнительно указывать в тестовых шаблонах.

#### 1.4.4 Разработки ИСП РАН

Исследования В области генерации тестовых программ ДЛЯ микропроцессоров ведутся в ИСП РАН с середины 2000-х годов [41]. В рамках этих исследований был разработан прототип инструмента MicroTESK (Microprocessor Testing and Specification Tool Kit) версии 1.0. Данный инструмент использует модели микропроцессора и тестовые шаблоны, разработанные на языке Java, и позволяет сгенерировать тесты для широкого спектра микропроцессорных архитектур при помощи случайных комбинаторных техник генерации, а также техник, основанных на разрешении ограничений. Модель микропроцессора включает в себя программный эмулятор, который позволяет отслеживать состояние микропроцессора в процессе генерации.

Модель микропроцессора задает семантику команд И структуру подсистемы управления памятью. Тестовые шаблоны позволяют описывать сценарии в терминах тестовых ситуаций, связанных с работой отдельных команд. При этом в тестовом шаблоне задаются используемые команды, их порядок и связанные с ними ситуации. Также инструмент позволяет строить тесты для тестирования работы модуля предсказания переходов (BPU, branch prediction unit) путем перебора возможных трасс выполнения в структуре переходов, заданной шаблоном [43]. Тесты для подсистемы управления памятью (MMU, memory management unit) описаются в виде коротких последовательностей команд (2-3 команды), для которых строятся комбинации возможных сценариев обработки обращений к памяти с учетом зависимостей (допустимых вариантов совместного использования буферов памяти) [63].

К достоинствам инструмента можно отнести: (1) возможность поддержки различных архитектур, (2) отсутствие зависимостей от внешних эмуляторов, (3) поддержку генерации нацеленных тестов для BPU и MMU. Главным недостатком инструмента является использование языка Java ДЛЯ моделирования шаблонов. Это И описания тестовых усложняет конфигурирование инструмента, т.к. требует знания языка Java и деталей реализации библиотек MicroTESK. При этом эмулятор и модель покрытия необходимо отдельно. Также описывать отсутствует возможность автоматического извлечения информации ИЗ описаний все свойства задавать в явном виде. Таким образом, микропроцессора приходится модели является трудноосуществимой задачей взаимодействия с разработчиками инструмента. Еще одна проблема, связанная с использованием языка Java, - это то, что обновления библиотек, которые неизбежны в процессе эволюции инструмента, могут повлечь за собой изменения в уже созданных моделях и шаблонах. Другой недостаток заключается в том, что в инструмент не заложена возможность интеграции новых методов генерации и их совместного использования. Например, нет возможности сгенерировать тестовую программу, решающую задачи тестирования BPU и MMU, на основе единого тестового шаблона.

#### 1.4.5 Другие разработки

#### Среда RDG

В компании Samsung разработана среда RDG (Random Diagnostics Generator) [64], предназначенная для случайной генерации тестовых программ для реконфигурируемых микропроцессоров (Samsung Reconfigurable Processor, SRP). Эта среда использует в качестве входных данных описание синтаксиса команд тестируемого микропроцессора и тестовые шаблоны на языке С++. Тестовые шаблоны задают, какие команды будут использованы в тестовой программе, и описывают ограничения, накладываемые на входные значения этих команд. Среда RDG не владеет информацией о семантике команд и не осуществляет исполнение тестовых программ  $\mathbf{c}$ целью предсказания результатов. Такой подход был выбран из-за особенностей тестирования реконфигурируемых микропроцессоров (система команд зависит конфигурации и их реализация может отличаться). Кроме того это позволяет с минимальными усилиями добавлять поддержку новых команд и обеспечить высокую скорость генерации. Недостаток такого подхода в том, что для генерации нацеленных тестов требуется описывать ограничения вручную и отсутствует возможность отслеживать состояние микропроцессора. Стоит RDG позволяет эффективно сказать, что инструмент решать задачу тестирования реконфигурируемых микропроцессоров Samsung, но он не является универсальным. Поддержка новых микропроцессорных архитектур и техник генерации в него не заложена.

# Генератор MA<sup>2</sup>TG

Исследования в области генерации тестовых программ для функциональной верификации микропроцессоров проводились в Оборонном научно-техническом университете Китая (National University of Defense

Technology) [65]. В рамках этих исследований был разработан прототип генератора тестовых программ MA<sup>2</sup>TG. Данный генератор применим для различных архитектур и поддерживает случайную генерацию и генерацию на основе ограничений. В качестве входных данных для генератора MA<sup>2</sup>TG используются спецификации на языке EXPRESSION [66], описывающие тестируемого микропроцессора, шаблоны архитектуру И на специализированном языке, формулирующие задачи генерации. Инструмент транслирует входные в файлы в программу-генератор на языке С++, которая В генерирует тесты. процессе генерации исполнения построенных последовательностей команд не осуществляется.

Спецификации на языке EXPRESSION содержат информацию структуре и поведенческих свойствах микропроцессора, а также о связи между ними. Для генерации тестовых программ в первую очередь необходима информация о поддерживаемых командах, которая включает текстовый и бинарный формат команд, списки их операндов и семантику команд (условия возникновения тестовых ситуаций). MA<sup>2</sup>TG строит на основе спецификаций библиотеку шаблонов команд (Instruction Template Library, ITL), которая используется при генерации. Каждая команда описывается классом на языке С++, который содержит методы для ее печати, получения списка аргументов и доступа к ассоциированным с ней ограничениям. Использование формальных спецификаций позволяет относительно просто сконфигурировать инструмент для тестирования микропроцессора с новой архитектурой. Однако подход  $MA^2TG$ имеет некоторые недостатки. Информация 0 структуре микропроцессора, спецификациях которая описывается В языке EXPRESSION, чаще всего не требуется для генерации тестовых программ. Эта информация может быть достаточно объемной, и ее специфицирование требует дополнительных трудозатрат. Кроме того она может быть недоступна на ранних стадиях работы над проектом. А в случаях, когда требуется тестирование микропроцессоров, по-разному реализующих одну и ту же использованию архитектуру, может препятствовать повторному она

спецификаций. Все это увеличивает трудоемкость разработки и поддержки спецификаций. Использование более простого языка, описывающего только поведенческие свойства, могло бы упростить эту задачу. Также, следует заметить, что MA<sup>2</sup>TG не строит эталонный эмулятор на основе спецификаций, хотя язык EXPRESSION предоставляет для этого достаточное количество информации. Эталонный эмулятор был бы полезен для проверки корректности построенных программ, создания встроенных проверок и разрешения ограничений.

Задачи генерации описываются на специализированном языке. Такие описания называют ограничениями (constraints), хотя, по сути, они являются вариантом тестовых шаблонов. На их основе MA<sup>2</sup>TG создает программы на языке C++, которые при помощи ITL и внешних библиотек разрешения ограничений, генерируют тесты. Язык описания тестовых шаблонов позволяет задавать следующие параметры: (1) используемые команды, их количество, порядок и вероятность появления; (2) ограничения на значения операндов команд; (3) зависимости по операндам между командами. Данный язык ориентирован на случайную выборку команд и разрешения ограничений для выбранных команд. Это позволяет быстро создавать большое количество небольших тестов для верификации определенных команд. Однако он не позволяет описывать сценарии со сложной структурой переходов. Также не предоставляется возможностей для описания многопоточных сценариев. Т.к. инструмент не осуществляет исполнение команд на эталонной модели, не поддерживается создание встроенных проверок. Кроме того отсутствие информации о состоянии микропроцессора усложняет решение ограничений. Из описания инструмента неясно, какие типы ограничений он поддерживает и насколько сложно в него добавить поддержку новых типов.

Инструмент MA<sup>2</sup>TG реализован в виде прототипа. Несмотря на то, что его подход имеет ряд преимуществ, его функциональные возможности ограничены. Остается непонятно насколько он соответствует требованиям, предъявляемым инструментам, используемым в промышленных проектах. Из

очевидных недостатков можно перечислить излишне детальные спецификации, отсутствие контроля состояния микропроцессора в процессе генерации, ограниченные возможности языка тестовых шаблонов и ограниченный набор поддерживаемых техник генерации.

# **Исследования Университета Флориды и Калифорнийского университета** в **Ирвайне**

В Университете Флориды (UFL) и Калифорнийском университет в генерации Ирвайне (UCI) был разработан метод тестовых программ, нацеленных на проверку корректности работы конвейера команд микропроцессора [37]. Данный метод использует спецификации на языке EXPRESSION [66], на основе которых строится модель, описывающая архитектуру микропроцессора в виде графа. Кроме этого разрабатывается модель ошибок, которая описывает типичные ошибки проектирования. На основе модели ошибок для модели микропроцессора строятся формулы, которые задают условия возникновения конкретных ошибок для данного микропроцессора. Для этих формул при помощи инструмента SMV (Symbolic Model Verifier) [66], который использует метод проверки моделей, стоятся тестовые примеры (контрпримеры для отрицания формул), на основе которых генерируются тестовые программы. По мнению авторов, метод масштабируется сложные микропроцессоры, на поэтому предлагается дополнительно использовать тестовые шаблоны. Они создаются вручную и содержат описания цепочек команд, которые вызывают определенные ситуации в поведении микропроцессора (прежде всего, конвейерные конфликты). К достоинствам данного метода можно отнести то, что он применим для типов микропроцессоров и позволяет обеспечить различных ситуаций в работе конвейера команд, используя минимальное количество тестов. Главный недостаток метода – сложность разработки детальных спецификаций и модели ошибок. Следует также отметить, что данные исследования носили академический характер и на их основе не были разработаны инструменты, которые могли бы использоваться в промышленных проектах.

# Инструмент µGP

Исследователями Туринского политехнического университета (Politecnico di Torino) был предложен интересный подход к генерации тестовых программ, основанный на использовании генетических алгоритмов [68, 69, 70]. Данный подход был реализован в прототипе инструмента µGP. Основная идея подхода состоит в следующем. Для генератора тестовых программ создается библиотека инструкций, которая описывает синтаксис языка ассемблера микропроцессора. Задачи генерации описываются в виде ациклического графа, который описывает поток выполнения тестовой программы. Каждая вершина графа содержит ссылку на описание команды в библиотеке команд и значения ее операндов. Библиотека команд и задачи генерации описываются на языке XML. Генерация тестовых программ осуществляется путем мутации структуры графа и значений операндов команд внутри отдельных вершин. Генератор пытается построить тестовую программу, которое обеспечит наилучшее покрытие для заданной метрики. Значение метрики получается путем выполнения построенных программ на программном эмуляторе RTL-модели.

Достоинством данного подхода является его гибкость и универсальность. Он позволяет достичь высокого уровня тестового покрытия для различных типов микропроцессоров, используя различные метрики покрытия. Главный недостаток — высокая вычислительная сложность, из-за которой скорость генерации получается достаточно низкой. Инструмент µGP реализует только один метод генерации и не предусматривает поддержку новых методов. Еще один возможный недостаток — это то, что входные форматы конфигурационных файлов не являются интуитивно понятными.

# 1.5 Выводы

Для всех рассмотренных в этой главе инструментов, независимо от поддерживаемых ими техник, можно выделить два свойства:

(1) реконфигурируемость и (2) расширяемость. Оба этих свойства показывают, какое количество усилий требуется для адаптации инструмента к решению новых задач. Под реконфигурируемость понимается возможность поддержки новых микропроцессорных архитектур, а под расширяемостью — возможность интеграции компонентов, реализующих различные техники генерации.

Другим важным свойством является контролируемость генерации, возможность отслеживать текущее состояние микропроцессора в процессе генерации путем исполнения генерируемых последовательностей команд на эталонной модели, в качестве которой выступает программный эмулятор. Это позволяет гарантировать корректность построенных программ, создавать тесты со встроенными проверками и применять техники генерации, использующие информацию о текущем состоянии микропроцессора. Эталонные модели разрабатываются отдельно от инструмента генерации и интегрируются в него при помощи специальных библиотек. Однако, по сути, они являются частью конфигурации инструмента т.к. используют знание о синтаксисе и семантике команд для их интерпретации.

Основным свойством, характеризующим техники генерации, является целенаправленность тестирования. Техники, основанные на случайной генерации, не позволяют систематическим образом обеспечить покрытие функциональных требований. Современные микропроцессоры с конвейерной архитектурой и сложной организацией памяти имеют огромное пространство возможных состояний, которые с малой вероятностью будут достигнуты при использовании случайных тестов. Поэтому для создания тестовых программ, нацеленных на проверку конкретных ситуаций или классов ситуаций, требуются специализированные техники, основанные на разрешении ограничений и проверке моделей.

Еще одним важным свойством современных инструментов верификации является возможность построения тестовых программ для многоядерных микропроцессоров. На базовом уровне она присутствует практически во всех инструментах, т.к. для этого достаточно включить в построенные программы

команды, обеспечивающие разветвление потока выполнения на несколько ядер. Однако техники нацеленной генерации, использующие информацию о текущем состоянии микропроцессора, должны учитывать тот факт, что каждое из ядер имеет свое состояние. Кроме того, инструменты должны обеспечивать покрытие ситуаций, связанных с параллельным выполнением программ.

Таблица 4 сравнивает функциональные возможности рассмотренных ранее инструментов по перечисленным критериям.

Таблица 4. Сравнение возможностей рассмотренных инструментов генерации

| Инструмент                    | Реконфигурируемость | Расширяемость | Контролируемость<br>генерации | Целенаправленность<br>тестирования | Поддержка<br>многоядерности |

|-------------------------------|---------------------|---------------|-------------------------------|------------------------------------|-----------------------------|

| MicroTESK 1.0                 | Да                  | Нет           | Да                            | Высокая                            | Нет                         |

| INTEG                         | Нет                 | Нет           | Нет                           | Средняя                            | Нет                         |

| RIS                           | Нет                 | Нет           | Нет                           | Средняя                            | Да                          |

| RAVEN                         | Да                  | Нет           | Да                            | Средняя                            | Да                          |

| Genesys-Pro, FPGen, DeepTrans | Да                  | Да (частично) | Да                            | Высокая                            | Да                          |

| RDG                           | Да                  | Нет           | Нет                           | Низкая                             | Нет                         |

| MA <sup>2</sup> TG            | Да                  | Нет           | Нет                           | Высокая                            | Нет                         |

| UFL/UCI                       | Да                  | Нет           | Нет                           | Высокая                            | Нет                         |

| μGP                           | Да                  | Нет           | Нет                           | Средняя                            | Нет                         |

Как можно заметить, большинство инструментов предназначено для решения конкретных задач и не предполагают расширяемость. Это объясняется тем, что коммерческие компании занимаются верификацией выпускаемых ими микропроцессоров и создают инструменты для решения текущих задач верификации, а исследовательские институты изобретают новые техники верификации и создают инструменты для их апробации. При этом задача интеграции техник, которые не используются в данный момент, не ставится.

Ситуация с реконфигурируемостью несколько сложнее. Несмотря на то, что некоторые инструменты позволяют конфигурирование под различные архитектуры, интеграция внешней эталонной модели сопряжена с трудностями. Большинство из перечисленных реконфигурируемых инструментов не

используют эталонные модели и не осуществляют контроль корректности построенных программ. Однако даже без необходимости интеграции эталонной модели создание пользовательских конфигураций может иметь значительную трудоемкость.

Целенаправленность тестирования и поддержка многоядерности характеризуют техники генерации и зависят от области применения инструмента. При этом они в той или иной степени связаны с расширяемостью и реконфигурируемость: более гибкие инструменты реализуют большее количество техник генерации и предоставляют больше возможностей.

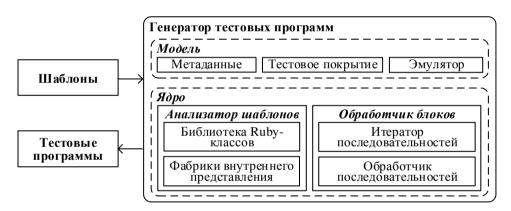

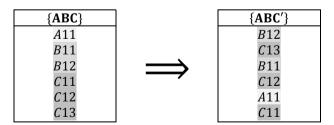

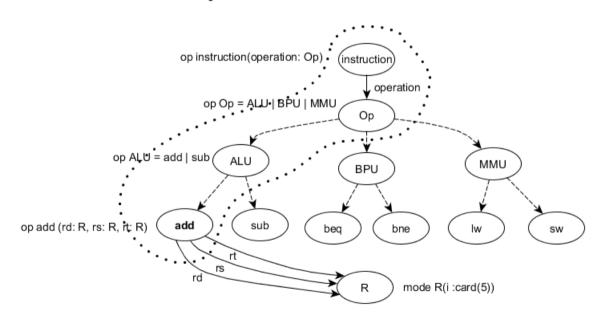

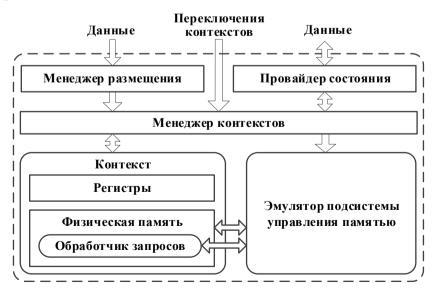

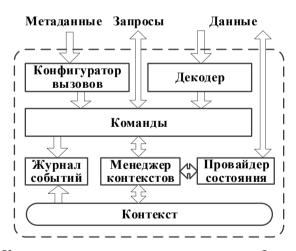

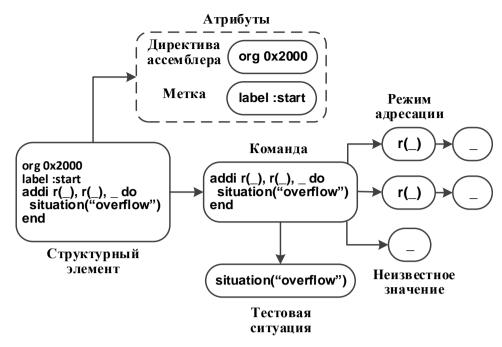

Т.к. применимость отдельных инструментов ограничена, актуальной задачей является создание инструмента, который позволил бы объединить различные методы генерации, и был бы применим для различных типов микропроцессоров. Подобный инструмент должен сочетать все перечисленные выше свойства. Его характеристики могут быть сформулированы следующим образом.